导语:

栅极接地NMOS是一种广泛应用的片上ESD器件结构,为达到特定ESD防护等级,一般会采用多叉指版图形式来减小器件占用的芯片面积。但是,多叉指栅极接地NMOS在ESD应力作用下,各个叉指难于做到均匀开启,无法达到预期ESD防护等级。本文从版图、器件结构、触发技术等角度介绍一些改善多叉指MOSFET静电防护器件电流泄放均匀性提升器件静电防护鲁棒性的技巧。

正文:

据文献报道,大面积叉指状静电箝制器件静电防护能力的提高并不与器件面积大小或器件叉指数目成正比。其根本原因是各个寄生三极管BJT的非均匀触发引发LDMOS器件中的电流聚集效应,导致了器件未能充分发挥防护潜能而过早失效。现有的改善多叉指MOSFET静电防护器件电流泄放均匀性的技巧包括版图布局、器件优化和增加触发电路等。

1、版图布局技巧

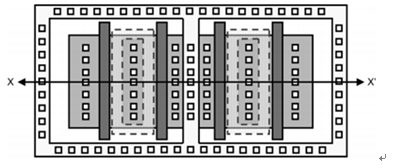

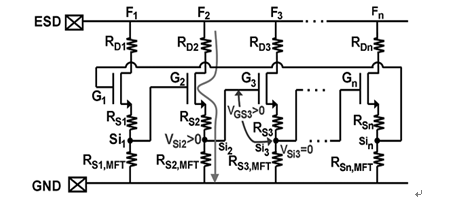

在传统多叉指LDNMOS器件的布局上,造成非均匀开启环境的主要原因来自寄生BJT基极电阻的差别。如图1所示为版图布局的改进,紧贴每一个NMOS管的源极插入一个P+型扩散区,可以使得多叉指NMOS器件中的每个横向NPN BJT的寄生电阻几乎接近相同。由于各个叉指具有几乎相同的基极电阻,其横向寄生NPN BJT可以几乎同时被触发开启。但是需要注意的是,各个源区由于P+扩散区的植入,布局的尺寸会有所增加;此外,如果各个叉指的衬底电阻因此而变得太小,那么所有寄生横向NPN BJT难以迅速开启保护内部电路器件的薄栅氧化层。

(a)

(b)

图1 (a)布局的顶视图;(b)X-X’方向截面图

2、栅极耦合技术

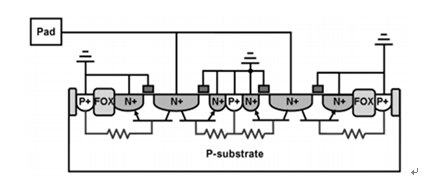

图2为一种采用栅极耦合技术的静电防护电路。通过不断调试电容和电阻的大小,在高ESD应力下,可以将一个合适的电压耦合到NMOS和PMOS的栅极,从而降低NMOS和PMOS的开启电压,大尺寸多叉指NMOS器件的非均匀开启问题可以通过栅极耦合技术得到克服。

然而对于NMOS和PMOS,如果耦合到栅极的偏置电压较高,会引起更多的沟道电流和较高的电场,使薄栅氧化层易于被破坏。所以,其ESD防护的鲁棒性会迅速减低。栅极耦合ESD防护电路必须仔细设计和优化,以防止ESD防护级别会因为栅极过驱动而下降。

图2 利用栅极耦合技术的ESD防护电路

3、衬底触发技术

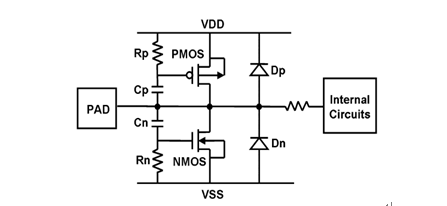

图3是采用衬底触发技术的ESD防护电路,同样通过调整电阻和电容,可以为横向寄生NPN BJT提供一个合适的衬底触发电压,降低NMOS管的触发电压,从而提升NMOS管的开启均匀性。

与栅极耦合的设计相比,衬底触发技术直接有效地提高了寄生BJT管的基极电压,因此,可有效防止沟道电流的产生和栅氧化层的过压问题。所以,衬底触发技术能持续提高ESD防护器件的ESD鲁棒性,而不像栅极耦合技术那样,在栅极过驱动的情况下出现鲁棒性降低。当然,该技术需要额外的版图面积来实现电容、电阻构成的触发电路。

图3 利用衬底触发技术的ESD防护电路

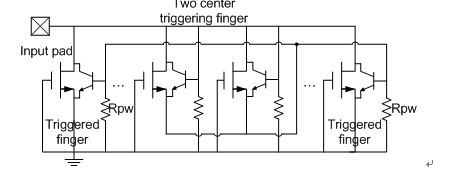

4、多米诺型触发技术

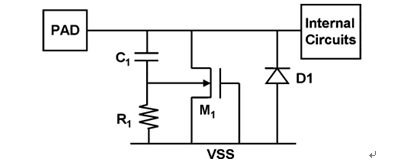

如图4所示为多米诺型多叉指器件触发技术。图中![]() 是漏极/源极的镇流电阻。每个叉指NMOS管中的电阻

是漏极/源极的镇流电阻。每个叉指NMOS管中的电阻![]() 用来给相邻叉指的栅极提供偏置电压。多米诺型结构中任意一个叉指被触发后,其它叉指会像多米诺骨牌一样,依次开启。假设F2指最先开启,那么,最开始的ESD电流将流过电阻

用来给相邻叉指的栅极提供偏置电压。多米诺型结构中任意一个叉指被触发后,其它叉指会像多米诺骨牌一样,依次开启。假设F2指最先开启,那么,最开始的ESD电流将流过电阻![]() ,形成

,形成![]() ,抬高F3栅极的电压。因此,根据栅极耦合效应,F3中内在的寄生BJT能够被触发从而导通。以此类推,依照相同的原理,源极的信号不断向下传递,使下一个管子触发。最终多指器件呈现整体性导通状态,从而高效泄放ESD电流。此电路中电阻若设计得当,可达到预期效果,但其布局实现较为复杂。

,抬高F3栅极的电压。因此,根据栅极耦合效应,F3中内在的寄生BJT能够被触发从而导通。以此类推,依照相同的原理,源极的信号不断向下传递,使下一个管子触发。最终多指器件呈现整体性导通状态,从而高效泄放ESD电流。此电路中电阻若设计得当,可达到预期效果,但其布局实现较为复杂。

图4 多米诺型多叉指器件的等效电路图

5、衬底自触发技术

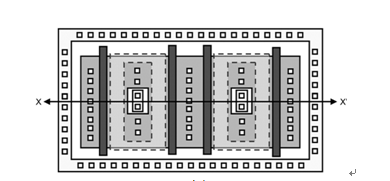

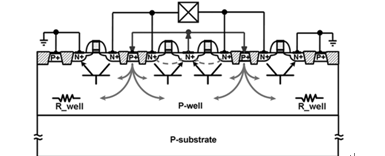

如图5所示为衬底自触发技术ESD防护电路的等效电路图。此改进的多叉指器件结构中间两个管子与两边的其它管子结构不完全相同,它利用中间两个叉指先行开启提供的电流作为衬底触发电流来启动其它叉指。除了中间叉指的源极与其它叉指寄生BJT的基极相接、而不是传统接地以外,中间两个叉指的尺寸大小、基本结构与传统的对称多指栅极接地MOS布局基本相同。

图5 衬底自触发ESD防护电路的等效电路图

图6(a)(b)分别为采用衬底自触发技术的栅极接地NMOS结构版图和X-X’方向的剖面图,此技术通过在各个叉指的漏极插入P+扩散区作为被触发衬底的节点。中间叉指的源极与这些被触发衬底节点相连接。在布局上,由于漏极区域一般要比源极区域大一些,插入P+扩散区并不会增加整个布局尺寸。

(a)

(b)

图6 栅极接地NMOS结构衬底自触发

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。